Yes, RMM recommends 20-50 Ohm for the gate resistor, but he kept quiet about the pulldown resistor. I don’t have a scope so I just kept reading what these R are for and how their value should be. This is not as easy as it looks, as both are often referred to as “gate resistor”. And the funniest calculation was this, which the author deemed as minimum knowledge needed about gate circuit resistance in MOSFETs. Well, he lost me at point 1…

So this was my train of thought:

Although frequency does not really matter in my design (no PWM), spikes will in all probability occur at switching. Now I’m not sure which of the two R prevent that, so my intention is to use both.

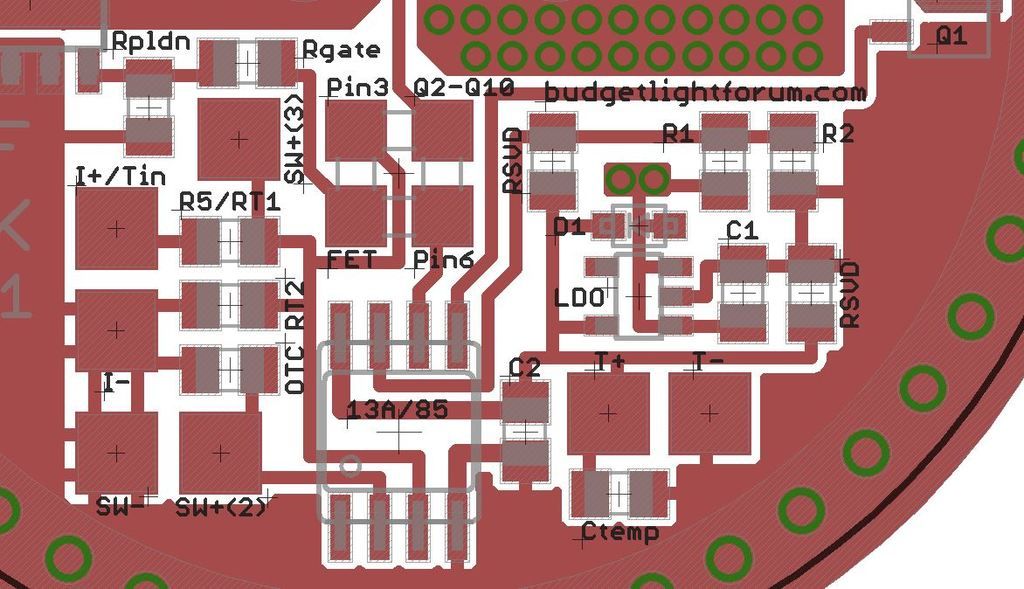

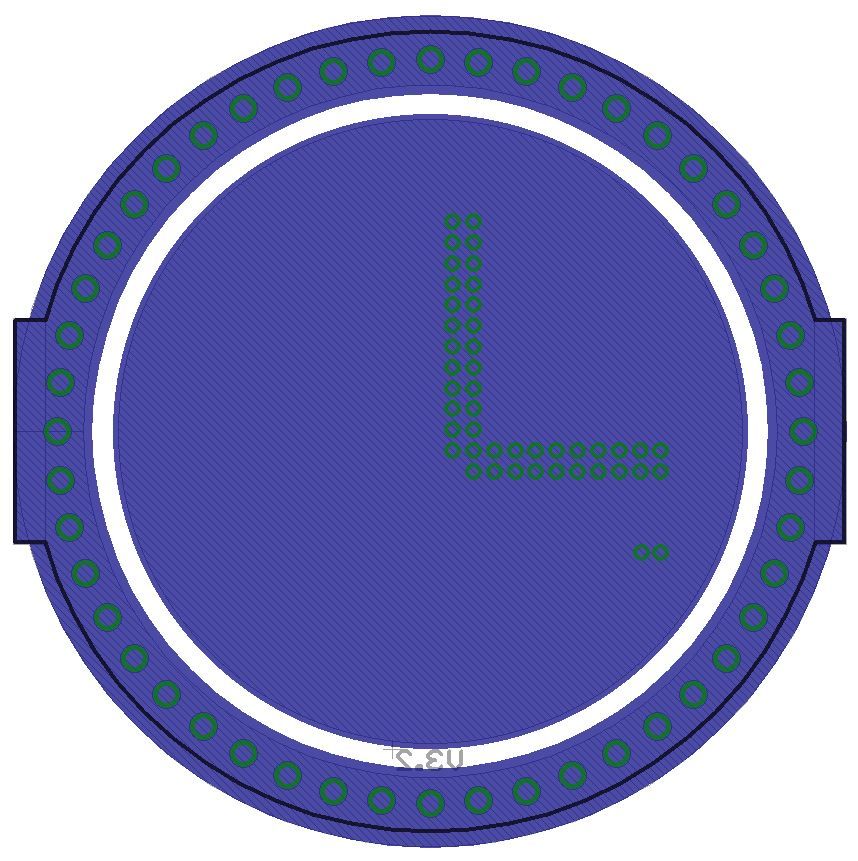

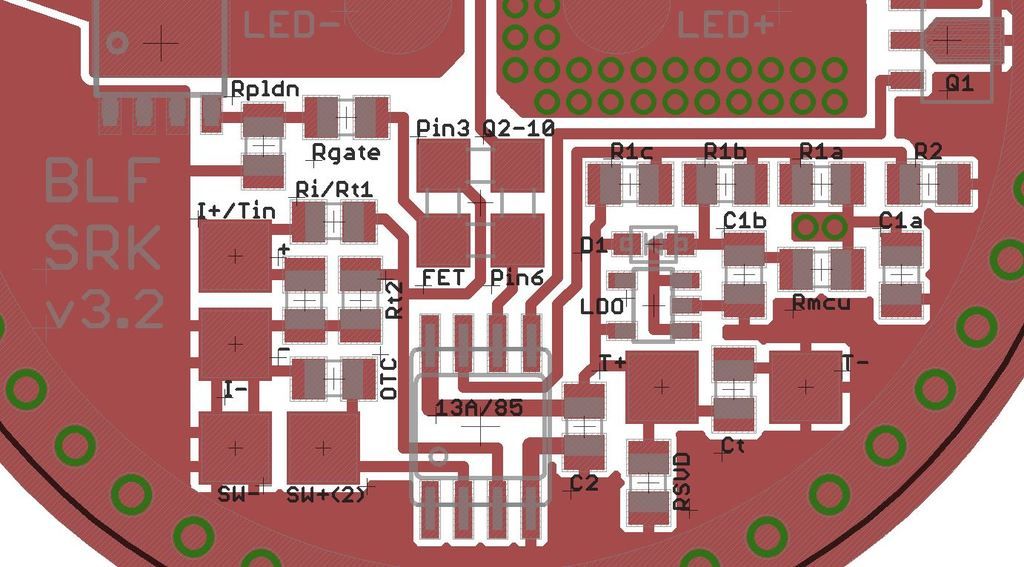

The pulldown resistor is said to be necessary to keep the gate from floating. Values between 1k, 10k and 100k ought to work. BLFers had good testing and scope results in the tens of kOhm, so I used the nearest I had which was 33kOhm.

The (series) gate resistor shall protect the output pin of the MCU by preventing overcurrent. There’s talk of values between 10 and 150 Ohm. I have no such value at hand… Well, the Attinys are said to have overcurrent protection although I couldn’t confirm it. But a lot of BLF FET driver were built without a gate resistor, so I dared to build it with a 0-Ohm-resistor for now. But I plan to use a gate resistor after my next parts order, because it might help preventing spikes, might protect the MCU and will not hurt the output. I thought of 50 Ohm, but I’m open to suggestions.

.

Err, another thing, while we’re talking resistors… R1 and R2 (LVP).

How high can we go to

- keep parasitic drain as low as possible

- while still get reliable voltage measuring from the MCU?

With my values of 33k/8k2 (I still prefer behind D1) I measure a parasitic drain at sleep_mode of 0.25mA. Now you use (before D1) 220k/47k for ages and probably with good measuring. One might think of even higher values, like 2M2/470k, 22M/4M7. Is there a limit where the MCU will not be able to measure the voltage anymore? Could that be calculated?